Based on the I3C basic specification from the MIPI Alliance, the DDR5 Sideband Bus is official known as JESD 403-1 JEDEC Module Sideband Bus. It is quite the upgrade from the System Management Bus based on I2C that was used for DDR4.

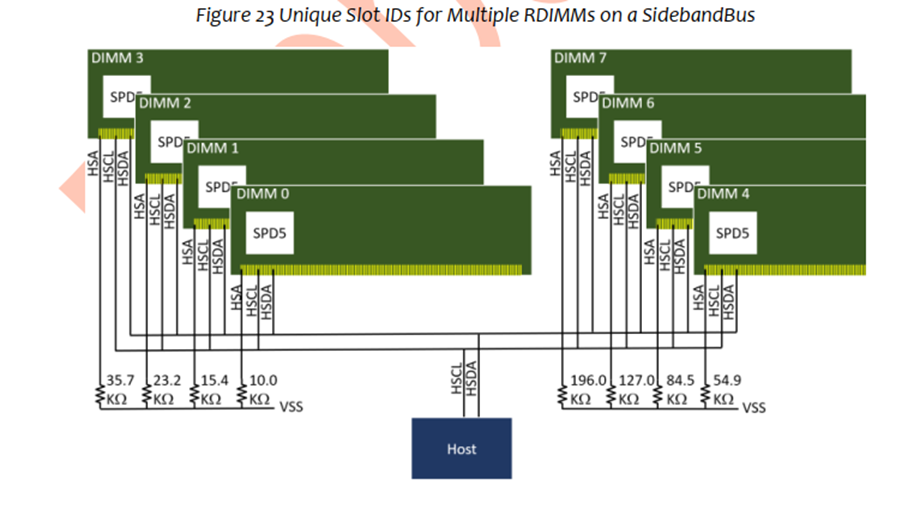

The NEW DDR5 Sideband Bus, drawing courtesy of JEDEC

. This bus connects all the functions on the DIMMs, RDIMMs, LRDIMMs and SODIMMs in various DDR5 system configurations. Each one of these devices (functions) has its own JEDEC specification. Designers also have to be aware that the bus itself has a specification (and the bus its based on, MIPI I3C, has a specification). In addition the SPD/Hub has two specifications as one is the device and the other is the contents. So counting them all up gives you 8 different specifications that you have to sift through to fully understand what is going on with this new bus.

Here is a list of all the specifications:

- JESD 403-1 JEDEC Module Sideband Bus

- MIPI I3C Basic specification

- JESD300-5 SPD5118, SPD5108 Hub and Serial Presence Detect Device Specification

- JESD400-5 DDR5 Serial Presence Detect Contents

- JESD301-2 PMIC5100 PMIC (UDIMM, SODIMM)

- JESD301-1 PMIC50x0 PMIC (RDIMM, LRDIMM, NVDIMM)

- JESD 302-1 TS5111, TS5110 Serial Bus Thermal Sensor Device Specification

- JESD82-511 DDR5RCD01 Registering Clock Driver

Typical DDR5 RDIMM Sideband Bus devices/functions

,SThe JESD 403-1 is now available for free on the JEDEC website

https://www.jedec.org/system/files/docs/JESD403-1-01.pdf

The basic architecture of the DDR5 Sideband bus is still a single controller that drives the bus with all the functions acting as responders. Although the MIPI specification allows for multiple controllers, through an arbitration mechanism, the JEDEC Task Group did not include multiple initiator operation. So for now only the memory controller can initiate traffic on this bus.

New for DDR5 is Voltage Regulators on DIMM so this is where the new PMIC (Power Management IC) parts come in. They have numerous registers and settings. The Temperature Sensors have been given a bit of an upgrade since DDR4 as has the SPD. The SPD now has a Hub as part of the device and it is here where the Host SDA and SCL is translated to the local SDA and SCL.

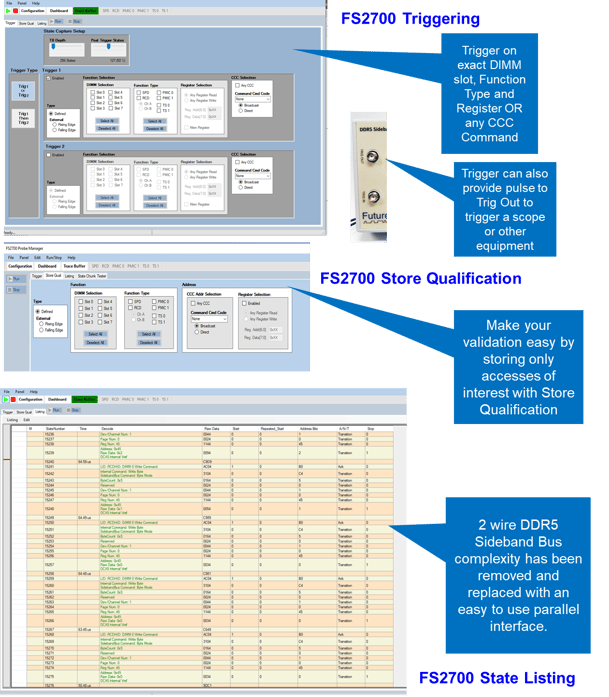

Helping our customers navigate each new Memory standard as it comes out is part of our Mission here at FuturePlus Systems and with that in mind the team has come up with a new product family for analyzing the DDR5 Sideband Bus.

- FS2700 DDR5 JEDEC Sideband Bus Protocol Analyzer

- FS2710 DDR5 JEDEC Sideband Bus Preprocessor for the Keysight U4164A

- FS2720 DDR5 JEDEC Sideband Bus Protocol Analyzer and Preprocessor (FS2700+FS2710)

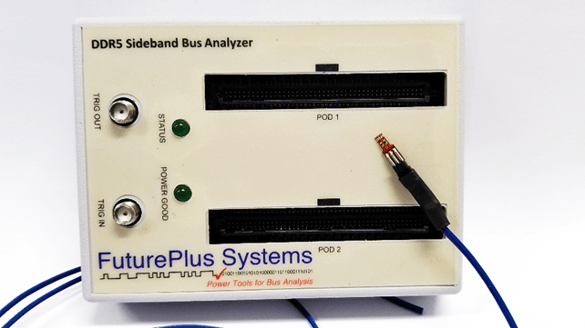

The FS2700 is for customers that want a small portable standalone version that does not require any help from a logic analyzer.

FS2700 Standalone DDR5 Sideband Bus Analyzer

The FS2710/FS2720 uses the triggering and trace of a Keysight U4164A logic analyzer. This option is available to engineers that want to correlate DDR5 bus traffic via our slot interposers.

FS2710/FS2720 DDR5 Sideband Bus Preprocessor

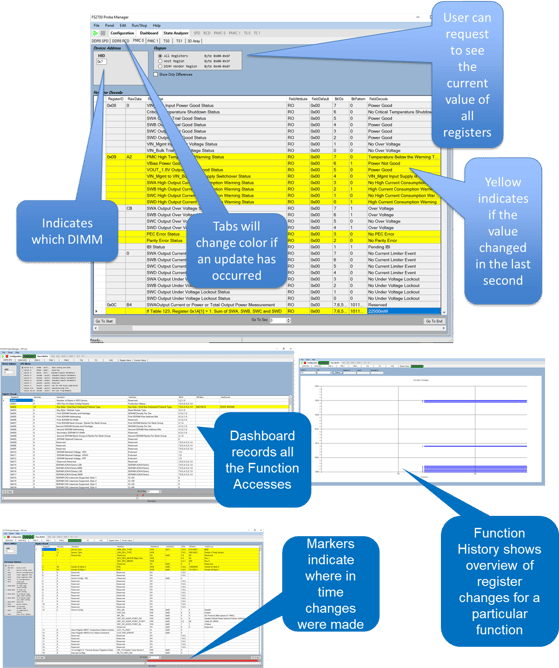

In addition to the traditional Trigger/Trace and Full Decode of all 8 specifications, the team has added a ‘Dashboard’ that contains a running tally of all functions on the bus and every register value!

New Dashboard feature stores the latest value of ALL the registers on the DDR5 Sideband Bus

How to attach to the DDR5 Sideband Bus

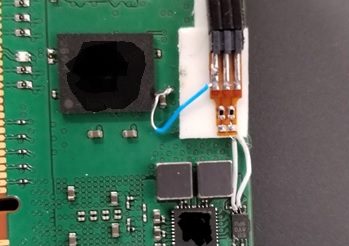

Probing the Host SDA and SCL signals can be a bit tricky. Don’t let the lower frequency of this bus (1Mhz to 12.5Mhz) fool you. This bus has to be treated carefully. The probing experts at FuturePlus have devised a nice little flex tip that users can attach where ever they can onto the HSDA and HSCL signals.

Probing HSDA and HSCL on a DDR5 RDIMM

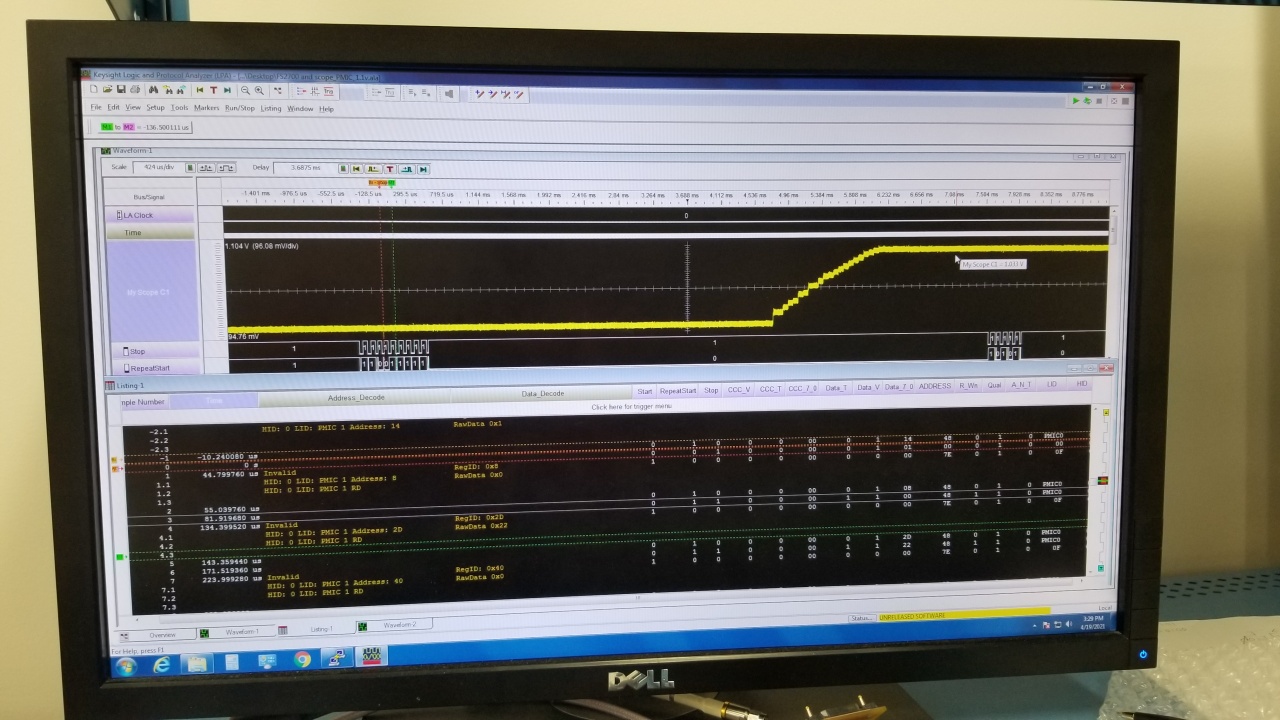

And how about triggering a scope?

The handy dandy TrigOut makes watching the power rails come up easy. Trigger on the appropriate PMIC register access and there it is!

The FS2710/FS2720 decoding the PMIC accesses and a scope tracing the DDR5 Power rails come up. Scope and Logic Analyzer courtesy of Keysight Technologies.

Summary

We here at FuturePlus have been working on DDR5 for 4 years now! We are ready with a full line of products and services to help your team be successful with this new technology. Contact us at protocol.decode@futureplus.com