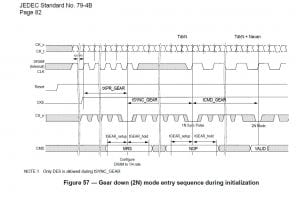

A Reliability, Availability and Serviceability (aka RAS) feature more clearly documented in the new JEDEC DDR4 Rev B spec, Gear-down mode, allows the DRAM Address/Command and Control bus to use every other rising clock of the DDR4 Memory bus clock.

The Memory Controller indicates that it wants the DRAM to operate in Gear-down mode by setting bit 3 in Mode Register 3 at boot time. The system then follows this operation with a sync pulse which is a single clock assertion of Chip Select. The DRAM then notes that sync pulse assertion and sync’s to that rising clock edge. It then uses every other rising edge of the clock after that. So even though the memory controller clock frequency has not changed the DRAM only uses every other edge.

Since the data uses both edges of the clock and now the DRAM Address/Command and Control uses every other edge of the rising clock they refer to it as ¼ rate or 2N. Normally the Address/Command/Control uses only the rising edge of the clock. This is called ½ rate.

Since the data uses both edges of the clock and now the DRAM Address/Command and Control uses every other edge of the rising clock they refer to it as ¼ rate or 2N. Normally the Address/Command/Control uses only the rising edge of the clock. This is called ½ rate.

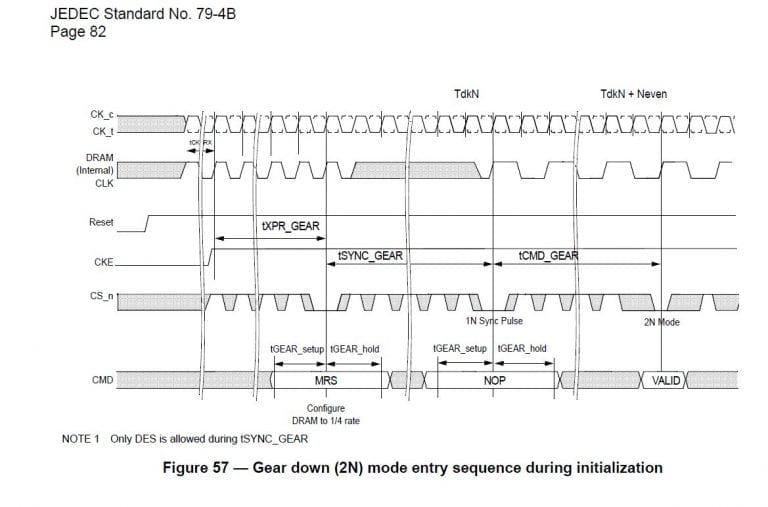

The screen shot below shows what the bus actually looks like from the memory controller’s point of view in Gear-down mode.

Waveform as seen on the FS2800 DDR Detective

Waveform as seen on the FS2800 DDR Detective

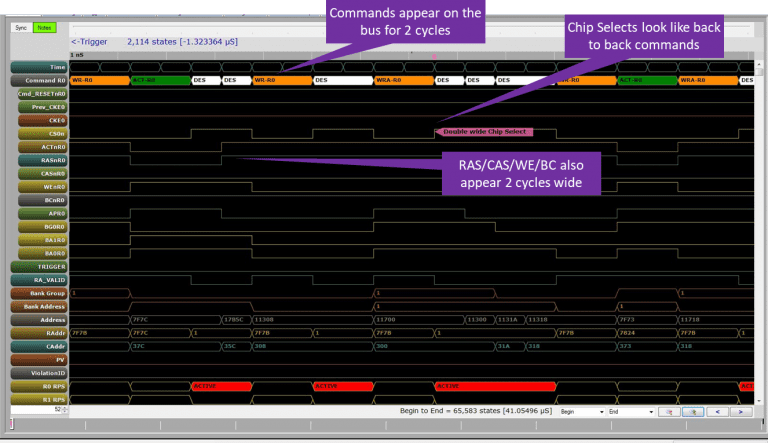

To reflect what the DRAM is actually using the test equipment needs to be able to adjust to gear-down mode and show what the DRAM is actually seeing on the DDR4 memory bus.

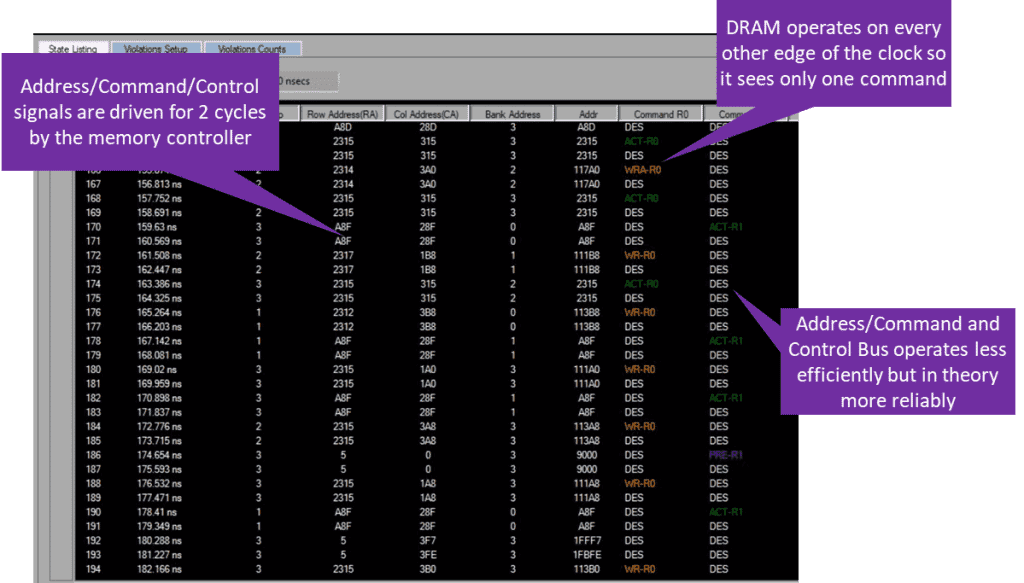

State Listing as seen on the FS2800 DDR Detective, what the DRAM sees for DDR4 bus operations while in gear-down mode.

State Listing as seen on the FS2800 DDR Detective, what the DRAM sees for DDR4 bus operations while in gear-down mode.

Some little nuances come to light when a system is operating in gear-down mode. One of them is that the timing between transactions has changed. All timing parameters are rounded up to an even number of clock cycles. This would also include all the protocol check parameters as they must also be rounded up to an even number also.

The screen shots shown are from an AMD Ryzen system operating in gear-down mode. If gear-down mode is not implemented correctly the DRAM will miss interpret bus transactions and memory corruption will occur. Here at FuturePlus we have never seen an Intel platform operate in gear-down mode and have seen nothing in the Intel documentation that would indicate that Intel processors support gear-down mode. However we do see the AMD Ryzen typically default (and is settable in the BIOS) to gear-down mode at 2666MT/s and above.

So what’s in your server? If you have memory issues give us a call. We sell equipment and services that will solve your DDR memory issues.