Having worked on and used the JEDEC DDR specifications for over 20 years we like to look for various improvements that each generation of these specifications bring. One of our favorites is clock stopping. For those of us in the Test and Measurement industry this is a frequent topic of discussion. State Mode (where we use the bus clock) is the most efficient use of trace memory and the best way to test if the memory bus is doing the right thing. Clock stopping tends to give us a bit of heart burn because if you have no clock all your logic stops. Now, when the clock stops, the bus is not doing anything anyways so you might think this is ok. However, we like to know how long the bus is stopped for. So, to do this we have to employ an alternate clock to help time these events. This might sound pretty straightforward, however, in the past the specifications were not really clear as to when the clock was allowed to stop, for how long, and when it can restart. In addition, many things need to happen before the clock is stopped, like closing all the banks, putting the DRAM into Self Refresh Mode, etc. So, from a test perspective we like to know EXACTLY when the clock will stop (give us a little warning please….) and when it will restart.

For DDR4 there was a signal called CKE (Clock Enable). This signal gave a hint as to when the clock was valid. However, it was also used to signal Power Down Entry and Exit while the clock was still running so it was not always a reliable indication of clock stoppage.

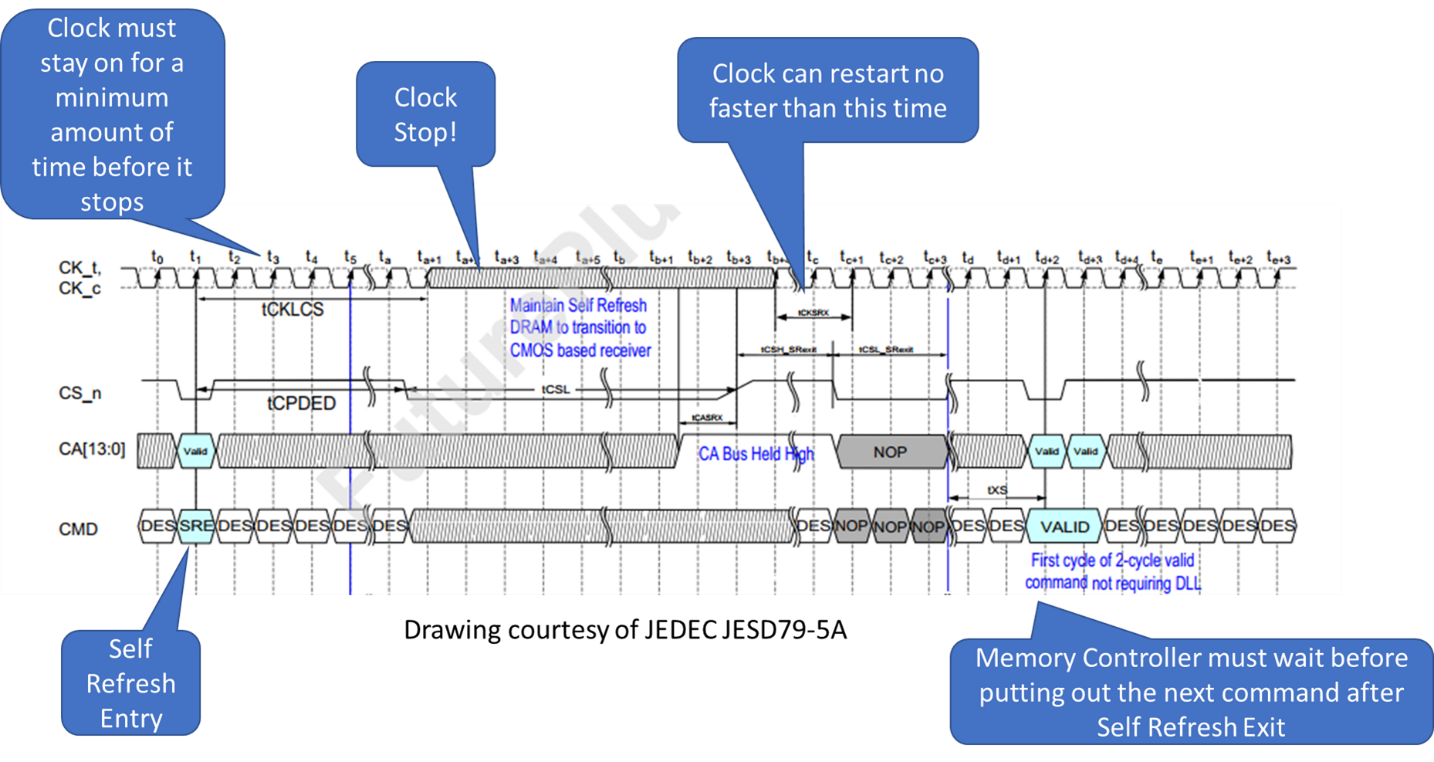

For DDR5 there is no Clock Enable signal as CKE was eliminated. So, perhaps the clock is not allowed to stop for DDR5? Not so! Clock stopping is an important power savings feature and indeed the DDR5 Memory Controller can stop the clock. For DDR5 this can only happen during a Self-Refresh. According to the DDR5 JESD79-5A specification the DRAM will turn off the internal clock to save power, so if the memory controller wants to also turn off the bus clock that is OK. However, the clock must stay on for a certain amount of time after going into Self Refresh (tCKLCS) and must be on for a certain amount of time before exiting Self Refresh (tCKSRX). In addition, there is a minimum time the Memory Controller can be in Self Refresh (tCSL). This process is outlined in the DDR5 DRAM specification so this will apply to embedded DDR5 and UDIMM and SODIMM applications. For Server class DIMMs, known as RDIMMs or LRDIMMs, we have to take a look at the DDR5 RCD specification.

It should also be noted that the clock frequency can change. The memory controller indicates this to the DRAM by executing a Self-Refresh with Frequency Change Command.

For RDIMMs and LRDIMMs the JESD82-511 (RCD01) specification is the guiding light. In this case the RCD handles the complexity. However, the Memory Controller signals ahead of time IF it intends to stop the clock or not during Self Refresh by using a pulse width modulation on the Chip Select signal.

It is interesting to note that during a clock stop the DDR5 Sideband Bus is alive and ticking and is unaffected by the clock stoppage.

So, there you have it! Clock stopping (and frequency changing) is alive and well on DDR5 (and better defined than previous generations). Now, let’s see who will implement it! Since we see lots of DDR5 systems in our line of work we will certainly let you know (not withstanding NDA’s!).